# 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office.

出 願 年 月 日 Date of Application:

2003年 4月15日

出 願 番 号 Application Number:

人

特願2003-110254

[ST. 10/C]:

[JP2003-110254]

出 願 Applicant(s):

株式会社東芝

特許庁長官 Commissioner, Japan Patent Office 2004年 1月27日

【書類名】

特許願

【整理番号】

APB0250241

【あて先】

特許庁長官殿

【国際特許分類】

H01L 21/027

G03F 1/08

【発明の名称】

パターン作成方法、パターン作成システム、および半導

体装置の製造方法

【請求項の数】

10

【発明者】

【住所又は居所】

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝

横浜事業所内

【氏名】

中野 亜矢子

【発明者】

【住所又は居所】

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝

横浜事業所内

【氏名】

小谷 敏也

【特許出願人】

【識別番号】

000003078

【氏名又は名称】

株式会社 東芝

【代理人】

【識別番号】

100083161

【弁理士】

【氏名又は名称】

外川 英明

【電話番号】

(03) 3457-2512

【手数料の表示】

【予納台帳番号】

010261

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【プルーフの要否】

要

### 【書類名】 明細書

【発明の名称】 パターン作成方法、パターン作成システム、および半導体装置の製造方法

#### 【特許請求の範囲】

【請求項1】 所定のデザインルールに従って作成した複数の露光マスクを使用 して半導体装置を製造するためのパターン作成方法において、

第1の露光マスクに配置される配線パターンから第1のターゲットパターンを抽出する第1の工程と、

第2の露光マスクに配置される配線パターンから前記第1のターゲットパターン と近接して配置される第2のターゲットパターンを抽出する第2の工程と、

前記第1および第2のターゲットパターンをそれぞれ半導体基板に転写するに際 し、前記第1および第2のターゲットパターンが、露光量と焦点距離の変動に対 するプロセス裕度の基準値を満たすか否かを判定する第3の工程と、

前記基準値を満たさない場合に、前記基準値を満たすように前記第1および第2のターゲットパターンのいずれか一方、または両方のターゲットパターンを補正する第4の工程と、

を有することを特徴とするパターン作成方法。

【請求項2】 前記第4の工程において、補正後の第1および第2のターゲットパターンが前記デザインルールを満たすように、前記第1および第2のターゲットパターンを補正することを特徴とする請求項1記載のパターン作成方法。

【請求項3】 前記第4の工程においては、前記第1の露光マスクの配線パターンのエッジと前記第2の露光マスクの配線パターンのエッジの距離を移動させることにより補正することを特徴とする請求項1記載のパターン作成方法。

【請求項4】 前記エッジの移動は、前記エッジの距離が予め定められた最小幅を満たしているエッジを移動させることを特徴とする請求項3記載のパターン作成方法。

【請求項5】 前記予め定めたルールは、シミュレーションまたは実験により定められることを特徴とする請求項1または請求項2のいずれか1項に記載のパターン作成方法。

【請求項6】 前記第2の工程において、前記第2のターゲットパターンが前記第1の露光マスクを除く複数の露光マスクのいずれか1つの露光マスクに配置されている配線パターン、または複数の露光マスクに跨って配置されている配線パターンを含むことを特徴とする請求項1乃至請求項5のいずれか1項に記載のパターン作成方法。

【請求項7】 前記第1のターゲットパターンが、コンタクト層、ビア層、メタル層、素子分離層、イオン注入層、またはゲート層の内のいずれかの層からなり、前記第2のターゲットパターンがコンタクト層、ビア層、メタル層、素子分離層、イオン注入層、またはゲート層の内から、前記第1のターゲットパターンとは異なるいずれかの層、または複数の層からなることを特徴とする請求項1乃至請求項6のいずれか1項に記載のパターン作成方法。

【請求項8】 前記第1または第2の露光マスクに配置され、前記補正された第 1または第2のターゲットパターンとは別の第1および第2のターゲットパターンを選択して、前記第1乃至第4の工程を繰り返すことを特徴とする前記請求項 1乃至請求項7のいずれか1項に記載のパターン作成方法。

【請求項9】 所定のデザインルールに従って作成した複数の露光マスクを使用 して半導体装置を製造するためのパターン作成システムにおいて、

第1の露光マスクに配置される配線パターンから第1のターゲットパターンを抽出する手段と、第2の露光マスクに配置される配線パターンから前記第1のターゲットパターンと近接して配置される第2のターゲットパターンを抽出する手段とを有するパターン抽出部と、

前記第1および第2のターゲットパターンが、露光量と焦点距離の変動に対する プロセス裕度の基準値を満たすか否かを判定する手段を有するパターン判定部と

前記基準値を満たさない場合に、前記基準値を満たすように前記第1および第2 のターゲットパターンのどちらか一方、または両方のターゲットパターンを変更 する手段を有するパターン変更部と、

を具備することを特徴とするパターン形成システム。

【請求項10】 所定のデザインルールに従って作成した複数の露光マスクを使

用して製造する半導体装置の製造方法において、

第1の露光マスクに配置される配線パターンから第1のターゲットパターンを抽出する第1工程と、

第2の露光マスクに配置される配線パターンから前記第1のターゲットパターン に近接して配置される第2のターゲットパターンを抽出する第2工程と、

前記第1および第2のターゲットパターンが、露光量と焦点距離の変動に対する プロセス裕度の基準値を満たすか否かを判定する第3工程と、

前記基準値を満たさない場合に、前記基準値を満たすように前記第1および第2 のターゲットパターンのどちらか一方、または両方を変更する第4工程と、

前記変更された配線パターンに基づいて露光マスクを製作する第5工程と、

前記露光マクスを用いたリソグラフィー工程を含む所定の半導体製造工程により 半導体装置を製造する第6工程と、

を有することを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

#### $[0\ 0\ 0\ 1]$

### 【発明の属する技術分野】

本発明は、マクスパターンに係わり、特に十分なプロセス裕度を有するパターンを形成するのに好適なパターン作成方法、該パターン作成システム、および該方法を用いた半導体装置の製造方法に関する。

### [00002]

#### 【従来の技術】

近年、半導体装置の高集積化、高速化に伴い半導体集積回路のパターン形成に 対する要求は非常に厳しいものがある。

#### [0003]

半導体集積回路において、設計製造が可能な最小の線幅を示すデザインルール は微細加工技術の向上と共に縮小され、100 n m以下の線幅を有する半導体集 積回路が製造されている。

### [0004]

このデザインルールを満たす範囲であれば、設計者は自由に回路パターンを設

計して配置することができる。

### [0005]

半導体集積回路は、半導体基板に形成された各種の膜材料をリソグラフィー技術によって形成したレジストパターンを用いて加工することを繰り返して製造される。このため、各露光マスクのパターン寸法や異なる露光マスク間の相対パターン寸法には一定の規則(パターンルール)が必要である。

### [0006]

例えば、半導体集積回路のレイアウトを設計する際のパターン配置の規則として、最小加工寸法、加工前後の寸法変化(加工変換差)、異なる露光マスクを重ねる時の合わせ精度などの規定が設けられる。

### [0007]

しかし、回路パターンが微細になるにつれて、半導体装置のリソグラフィー工程で、露光マクス上に形成されたパターンを半導体基板に転写する際に、光近接効果(OPE:Optical Proximity Effect)により回路の設計寸法と実際に半導体基板に転写された寸法とのずれが無視できなくなり、半導体装置の特性に影響を与えるようになってきた。

### [0008]

例えば、デザインルールを満たすパターンであっても、パターン中の鋭利な部分は転写されずに角がとれて丸くなり、あるいはラインパターンの疎密分布によりライン寸法が変化してしまうことがある。

#### [0009]

このずれを減ずる方法として、光学シミュレーションにより露光マクス上のパターン寸法を、例えば、部分的にパターン幅を太くしたり、あるいはダミーパターンを配したりして、補正する方法(OPC:Optical Proximity Correction)が知られている。

#### [0010]

しかしながら、このOPCは半導体基板に形成されるパターンが設計パターン 寸法通りになるように露光マスク上のパターン寸法を補正するものであり、リソ グラフィー工程でのプロセスマージンを増加させるものではない。

### $[0\ 0\ 1\ 1]$

従って、パターンを半導体基板に転写する際に、露光パラメータ、例えば、露 光量や焦点距離が適正値から変動しても、そのパターンが半導体装置の特性上問 題にならない寸法で形成される許容範囲を示すプロセス裕度が基準値に満たない パターンに対しては効果がない。

### $[0\ 0\ 1\ 2]$

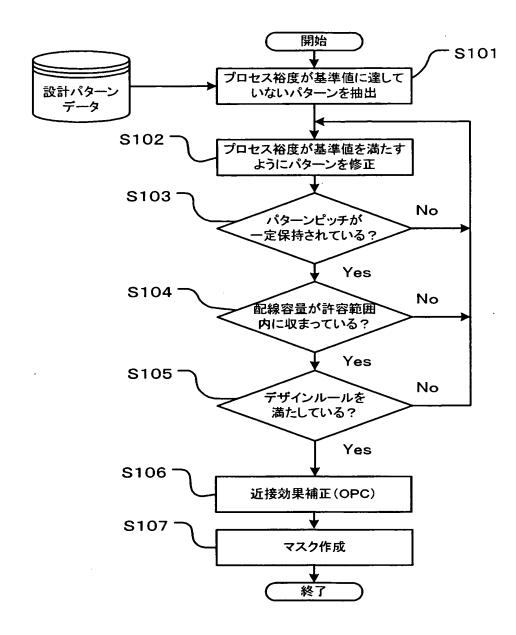

この問題を解決するパターン作成方法が知られている(例えば、特許文献 1 参照。)。

### $[0\ 0\ 1\ 3]$

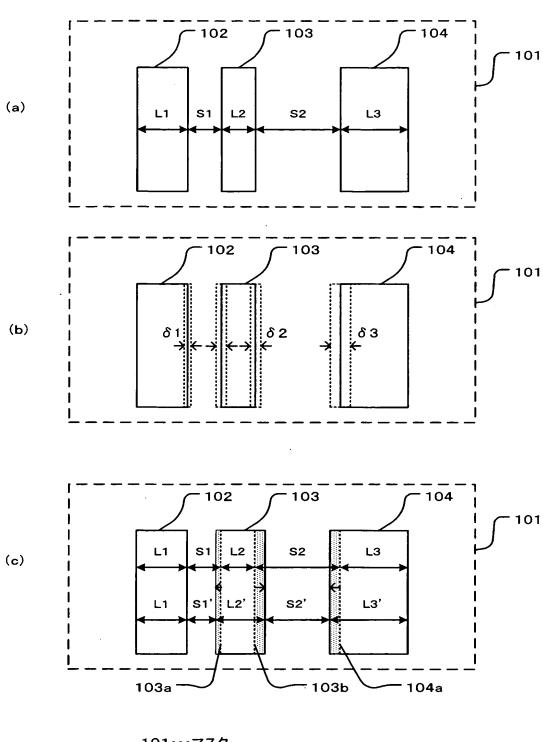

この特許文献1に開示されたパターン作成方法について、図12および図13を用いて説明する。図12はこのパターン作成方法の全体構成を示すフローチャート、図13(a)は配線パターンの補正前の状態を示すレイアウト図、図13(b)は図13(a)に示した配線パターンに対して露光量および焦点距離の条件を振ったときの最大ライン寸法および最小ライン寸法の転写パターンを示すレイアウト図、図13(c)は図13(a)に示した配線パターンの補正後の状態を示すレイアウト図である。

#### $[0\ 0\ 1\ 4]$

図12および図13に示すように、この配線パターンはラインとスペースで構成されており、露光マスク101上に、ライン寸法L1の配線パターン102と、スペース寸法S1を隔てたライン寸法L2の配線パターン103と、スペース寸法S2を隔てたライン寸法L3の配線パターン104が平行に配置されている。

#### [0015]

初めに、この設計パターンデータをデータ記録装置から読み込み、ラインとスペースの関係から得られるプロセス裕度が基準値に達していない配線パターンを設計パターンから抽出する。

#### $[0\ 0\ 1\ 6\ ]$

即ち、露光量と焦点距離を所定量振ったリソグラフィー・シミュレーションを おこない、配線パターン102のライン寸法L1の変動量 δ1、配線パターン1 03のライン寸法L2の変動量 δ2、および配線パターン104のライン寸法L 3の変動量 δ3を求める。

### $[0\ 0\ 1\ 7]$

特許文献では、δ1よりδ2、δ3が大きく、配線パターン103、104の プロセス裕度が基準値を満たしていないと判定されるものとしている(ステップ S101)。

### [0018]

次に、プロセス裕度が基準値を満たすように、配線パターン103の両側のエッジ103a、103bを移動してライン寸法L2をL2´に拡げ、配線パターン104の片側のエッジ104aを移動してライン寸法L3をL3´に拡げて、配線パターンを補正している(ステップS102)。

### [0019]

そして、配線パターンを補正した後、配線パターンのピッチが一定に保持されているか否かのチェックがおこなわれる(ステップS103)。

### [0020]

配線パターンのピッチが一定に保持されていない場合は、ステップS102に戻り、補正前後で配線パターンのピッチが一定に保持されるように、ライン寸法の補正量に応じてスペース寸法S1をS1´に狭め、スペース寸法S2をS2´に狭めて、再度パターンの補正がおこなわれる。

### [0021]

次に、補正後の配線パターンの配線容量が許容範囲に収まっているか否かを判定する。配線パターンのプロセス裕度を補正する場合、ライン寸法を拡げることで多層配線においては、上層あるいは下層の配線間で生じる寄生容量(配線容量)が許容値を超えてしまうことが考えられるためである(ステップS104)。

#### [0022]

配線容量が許容範囲に収まっていない場合は、ステップS102に戻り、配線容量が許容範囲に収まるように再度パターンを補正する。

#### [0023]

配線容量が許容範囲に収まっている場合は、補正後の配線パターンがデザイン

ルールを満たしているか否かを判定する。即ち、補正後の配線パターンのライン 寸法およびスペース寸法がデザインルールで規定する最小ライン寸法および最小 スペース寸法以上であるかを判定する(ステップS105)。

#### [0024]

補正後の配線パターンがデザインルールを満たしていない場合は、ステップS 102に戻り、デザインルールを満たすように再度パターンを補正する。

### [0025]

補正後の配線パターンがデザインルールを満たしている場合は、補正後の配線パターンの必要な箇所に対して近接効果補正(OPC)をおこなう(ステップS106)。

### [0026]

最後に、補正された設計パターンデータに基づいて露光マスクを作成している (ステップS107)。

### [0027]

また、別の実施の形態では、コンタクトホールパターンと隣接するコンタクトホールパターン間のスペースとの関係に着目し、そのコンタクトホールパターンのプロセス裕度が基準値を満たさないパターンを抽出して、それがプロセス裕度を満たすように補正する方法を開示している。

#### $[0\ 0\ 2\ 8]$

以上説明したように、特許文献1に開示されたパターンの作成方法は、同一の 露光マスク上に配置される配線パターン(ラインパターン)あるいはコンタクト ホールパターンのように同一露光マスク中のパターンのプロセス裕度を改善する ものである。

### [0029]

従って、半導体基板へのパターン転写の高精度化が要求され、高集積化される 半導体装置の製造にはさらなる技術の開発が必要であった。

#### [0030]

#### 【特許文献1】

特開2002-131882号公報(5-8頁、図2)

### [0031]

### 【発明が解決しようとする課題】

上述のパターン作成方法では、複数の露光マスクに跨って配置される配線パターン間のプロセス裕度の向上には適用できない問題がある。

### [0032]

本発明は、上記問題点を解決するためになされたもので、複数の露光マスクに 跨って配置される配線パターン間のプロセス裕度を向上させることができるパタ ーン作成方法、該パターン作成システム、および該方法を用いた半導体装置の製 造方法を提供することを目的とする。

### [0033]

#### 【課題を解決するための手段】

上記目的を達成するために、本発明の一態様のパターン作成方法では、所定のデザインルールに従って作成した複数の露光マスクを使用して半導体装置を製造するためのパターン作成方法において、第1の露光マスクに配置される配線パターンから第1のターゲットパターンを抽出する第1の工程と、第2の露光マスクに配置される配線パターンから前記第1のターゲットパターンと近接して配置される第2のターゲットパターンを抽出する第2の工程と、前記第1および第2のターゲットパターンをそれぞれ半導体基板に転写するに際し、前記第1および第2のターゲットパターンが、露光量と焦点距離の変動に対するプロセス裕度の基準値を満たすか否かを判定する第3の工程と、前記基準値を満たさない場合に、前記基準値を満たすように前記第1および第2のターゲットパターンのいずれか一方、または両方のターゲットパターンを補正する第4の工程とを有することを特徴としている。

#### $[0\ 0\ 3\ 4]$

また、本発明の一態様のパターン作成システムでは、所定のデザインルールに 従って作成した複数の露光マスクを使用して半導体装置を製造するためのパター ン作成システムにおいて、第1の露光マスクに配置される配線パターンから第1 のターゲットパターンを抽出する手段と、第2の露光マスクに配置される配線パ ターンから前記第1のターゲットパターンと近接して配置される第2のターゲッ

9/

トパターンを抽出する手段とを有するパターン抽出部と、前記第1および第2のターゲットパターンが、露光量と焦点距離の変動に対するプロセス裕度の基準値を満たすか否かを判定する手段を有するパターン判定部と、前記基準値を満たさない場合に、前記基準値を満たすように前記第1および第2のターゲットパターンのどちらか一方、または両方のターゲットパターンを変更する手段を有するパターン変更部とを具備することを特徴としている。

### [0035]

更に、本発明の一態様の半導体装置の製造方法では、所定のデザインルールに従って作成した複数の露光マスクを使用して製造する半導体装置の製造方法において、第1の露光マスクに配置される配線パターンから第1のターゲットパターンを抽出する第1工程と、第2の露光マスクに配置される配線パターンから前記第1のターゲットパターンに近接して配置される第2のターゲットパターンを抽出する第2工程と、前記第1および第2のターゲットパターンが、露光量と焦点距離の変動に対するプロセス裕度の基準値を満たすか否かを判定する第3工程と、前記基準値を満たさない場合に、前記基準値を満たすように前記第1および第2のターゲットパターンのどちらか一方、または両方を変更する第4工程と、前記変更されたパターンに基づいて露光マスクを製作する第5工程と、前記露光マクスを用いたリソグラフィー工程を含む所定の半導体製造工程により半導体装置を製造する第6工程とを有することを特徴としている。

### [0036]

#### 【発明の実施の形態】

以下、本発明の実施の形態に係わるパターン作成方法について、図面を参照しながら説明する。

#### [0037]

#### (第1の実施の形態)

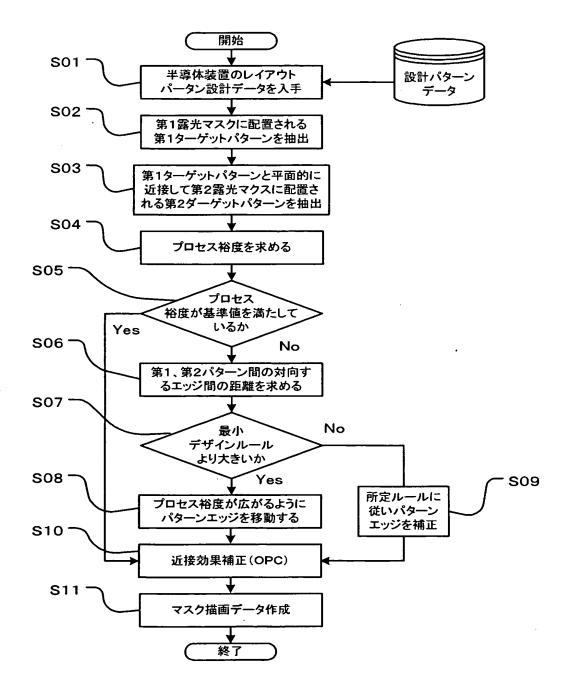

図1は、本発明の第1の実施の形態に係わるパターン作成方法で、半導体装置の設計パターンデータから露光マスク描画データが作成されるまでの工程を示すフローチャートである。

### [0038]

図1に示すように、まず、所定のデザインルールに従って半導体基板に形成される半導体装置のレイアウトパターンの設計データが設計パターンデータ記録装置から入手され(ステップS 0 1)、その設計データから、任意の配線パターンが選び出だされる。この選出された配線パターンは、複数の露光マクスにそれぞれ配置されるパターンデータから構成されている。

### [0039]

始めに、第1の露光マクスに配置されるパターンの中から、プロセス裕度がチェックされる第1のターゲットパターンが抽出される(ステップS02)。

### [0040]

次に、第1のターゲットパターンに近接して第2の露光マスクに配置される第 2のターゲットパターンが抽出される(ステップS03)。

### [0041]

そして、第1および第2のターゲットパターンがウェーハ上に転写される際に、露光パラメータの条件変動により生じるパターンの変動量に対してプロセス裕度を求める(ステップS04)。

### [0042]

このプロセス裕度とは、例えば、リソグラフィー・シミュレーションにより露 光量や焦点距離を所定範囲内で振ったときの最大パターン寸法と最小パターン寸 法との差から求まるものである。

### [0043]

次に、ステップS05において、このプロセス裕度が予め与えられた基準値を満たすか否かが判定され、基準値を満たしていない場合には、パターンを補正する必要があり、ステップS06へ進み、基準値を満たしている場合には、パターンを補正する必要がないので、ステップS10へジャンプする。

#### $[0\ 0\ 4\ 4\ ]$

次に、プロセス裕度が基準値を満たしていない場合には、第1のターゲットパターンと第2のターゲットパターン間の距離が求められ(ステップS06)、その距離が最小デザインルールより大きいか否かがさらに判定される(ステップS07)。

### [0045]

ここでの最小デザインルールとは、ターゲットパターンが存在する半導体装置 のデザインルールのうち、ターゲットパターンの存在するレイヤー中のデザイン ルールの最小値のことを言う。

### [0046]

そして、この距離が最小デザインルールより大きい場合には、プロセス裕度が基準値より広がるようにパターンエッジを移動させて補正された新しいパターンを形成し(ステップS08)、一方、最小デザインルールより小さい場合には、予めリソグラフィー・シミュレーション、あるいは、実験によりデバイス特性に影響を及ぼさない範囲でパターンを補正するためのルールを作成し、その所定ルールに従いパターンエッジが補正される(ステップS09)。

### [0047]

いずれの場合においても最後に、パターンの近接効果補正(OPC)が施され (ステップS10)、露光マスク描画データが作成される(ステップS11)。

### [0048]

さらに、上述したパターン形成工程は、設計データにある全ての配線パターンに対して繰り返され、最終的に露光マスクに描画される露光マスクデータとなる。

### [0049]

次に、上述のパターン作成方法により配線パターンを補正し、プロセス裕度を 改善する場合について、具体的に説明する。

#### $[0\ 0\ 5\ 0]$

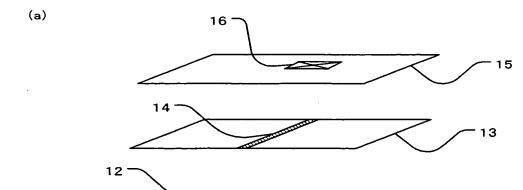

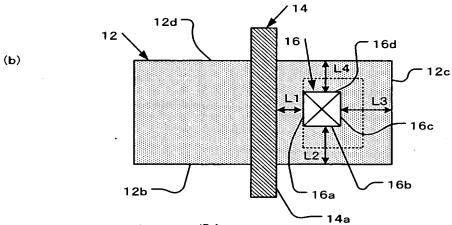

図2は、半導体装置のリソグラフィー工程で用いられる露光マスクを示す図で、図2(a)は、3数の露光マスクにそれぞれ形成される配線パターンの要部を示す外観図、図2(b)は、図2(a)の露光マスクを重ねて得られる配線パターンで、イオン注入による拡散層と、ゲート配線と、コンタクトホールが近接して配置されたパターンの例である。

#### [0051]

図2(a)に示すように、第1の露光マスク11にイオン注入による拡散層を

形成するためのイオン注入層パターン12と、第2の露光マスク13にゲート配線を形成するためのゲート配線パターン14と、および第3の露光マスク15にコンタクトホールを形成するためのコンタクトホールパターン16がそれぞれ形成されている。

### [0052]

即ち、リソグラフィー技術により、第1の露光マスク11を用いて、レジスト膜を形成した半導体基板の所定領域にイオン注入層パターン12が開口されてイオン注入および活性化処理がなされ、次に、半導体基板に絶縁膜およびゲート配線膜を形成した後、第2の露光マスク13を用いてゲート配線膜にゲート配線パターン14が加工され、更に、第3の露光マスク15を用いて絶縁膜にコンタクトホールパターン16が開口される。

### [0053]

ここで、図2(b)に示すように、第1の露光マスク11のコンタクトホールパターン16の各エッジ16a、16b、16c、16dと、それぞれに近接して対向配置される第2の露光マスク13のゲート配線パターン14の各エッジ14a、14b、および第3の露光マスク15のイオン注入パターン12の各エッジ12a、12b、12c、12dとから構成される配線パターンにおいて、コンタクトホールパターン16のエッジ16aとゲート配線パターン14のエッジ14aの距離をL1、同じくエッジ16bとエッジ12bの距離をL2、同じくエッジ16cとエッジ12cの距離をL3、同じくエッジ16dとエッジ12dの距離をL4とする。

#### [0054]

図1に示したフローチャートに従い、第3の露光マスク15のコンタクトホールパターン16がリソグラフィー工程でプロセス裕度が基準値より少ないと判断された場合には、露光マスク間の設計パターン距離(L1、L2、L3、L4)が求められ、その結果に基づいてプロセス裕度が大きくなるように新しい配線パターンを形成するのための補正処理が行われる。

### [0055]

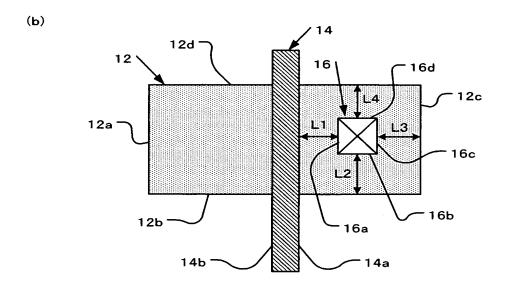

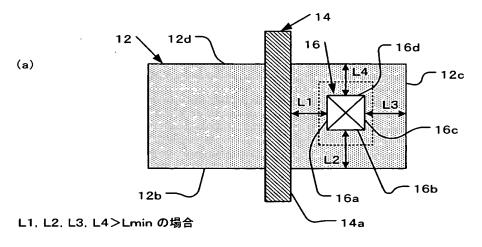

図3は配線パターンの変更ルールを説明するための図で、例えば、図3(a)

に示すように、L1、L2、L3、L4が全て最小デザインルール(Lmin) より大きい場合には、コンタクトホールパターン16の各エッジ16a、16b、16c、16dをそれぞれエッジ12a、12b、12c、12dの方向へ移動してコンタクトホールパターン16の寸法を大きくして、プロセス裕度を基準値より大きくする。

### [0056]

また、図3(b)に示すように、コンタクトホールパターン16のエッジ16 a とゲート配線パターン14のエッジ14 a の距離L1がLminである場合には、エッジ16 a を固定し、他のエッジ16 b、16 c、16 dをそれぞれエッジ12 b、12 c、12 dの方向へ移動してコンタクトホールパターン16の寸法を大きくすることにより、プロセス裕度を基準値より大きくする。

### [0057]

更に、図3(c)に示すように、コンタクトホールパターン16のエッジ16 Cとイオン注入パターン12のエッジ12cとの距離L3がLminである場合には、エッジ16cを固定し、他のエッジ16a、16b、16dをそれぞれエッジ12a、12b、12dの方向へ移動してコンタクトホールパターン16の寸法を大きくすることにより、プロセス裕度を基準値より大きくする。

#### [0058]

更に、また、コンタクトホールパターン16のエッジ16bとイオン注入パターン12のエッジ12bとの距離L2やコンタクトホールパターン16のエッジ16dとイオン注入パターン12のエッジ12dとの距離L4、あるいは複数のLがLminである場合には、同様に他のLがLminより大きなエッジを移動してコンタクトホールパターン16の寸法を大きくして、プロセス裕度を基準値より大きくする。

#### [0059]

ここで、各エッジの移動量は各距離L1、L2、L3、L4が最小デザインルールに等しくなるところを上限として、シミュレーションまた実験により状況に応じて定めている。

#### [0060]

以上説明したように、本発明の第1の実施の形態に係わるパターン作成方法では、複数の露光マクスに跨がり、且つ、近接して配置される配線パターンを抽出して、その配線パターン間の距離に応じたパターンの補正を行うことにより、配線パターン間のプロセス裕度が向上する。従って、半導体基板への配線パターンの転写精度が向上し、半導体装置の製造が容易になる。

### $[0\ 0\ 6\ 1]$

なお、上述の実施の形態では、第1の露光マスク11にイオン注入層パターン 12と、第2の露光マスク13にゲート配線パターン14と、および第3の露光 マスク15にコンタクトホールパターン16がそれぞれ形成されている場合について説明したが、パターンをビア層、メタル層、素子分離層、ゲート層等としても構わない。以下に、これらの変形例を説明する。

### [0062]

### (第1の実施の形態の変形例1)

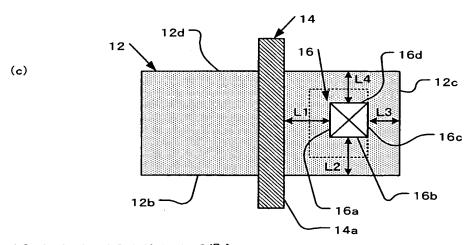

図4は本発明の第1の実施の形態の変形例1を示す配線パターンである。本変形例が第1の実施の形態と異なる点は、メタル配線ラインにビアホールが形成される配線パターンとしたことにあり、第2の露光マスク13にメタル配線パターン24、および第3の露光マスク15にビアホールパターン26が形成されている。なお、本変形例においては、第1の実施の形態に対応させて配線パターンが設けられる露光マスクを第2の露光マスク、またホールパターンが形成される露光マスクを第3の露光マスクと呼称しているが、3枚の露光マスクが存在するのではなく、2枚の露光マスクからなる。

#### $[0\ 0\ 6\ 3]$

即ち、図4に示すように、リソグラフィー技術により、メタル配線膜を形成した半導体基板の所定領域に第2の露光マスク13を用いてメタル配線パターン24が加工され、第3の露光マスク15を用いてメタル配線にビアホールパターン26が開口される。

#### [0064]

ここで、第2の露光マスク13のメタル配線パターン24の各エッジ24a、 24b、24c、24dと、第3の露光マスク15のビアホールパターン26の 各エッジ26a、26b、26c、26dとから構成される配線パターンにおいて、エッジ24aとエッジ26aの距離をL1、エッジ24bとエッジ26bの 距離をL2、エッジ24cとエッジ26cの距離をL3、エッジ24dとエッジ 26dの距離をL4とする。

### [0065]

図1に示したフローチャートに従って、第3の露光マスク15のビアホールパターン26がリソグラフィー工程でプロセス裕度が基準値より少ないと判断されると、第2露光マスク13と第3の露光マスク15間の設計パターン距離(L1、L2、L3、L4)が求められ、その結果に基づいてプロセス裕度が基準値より大きくなるように新しいパターンを形成するのための補正処理が行われる。

### [0066]

例えば、メタル配線パターン24のエッジ24bとビアホールパターン26のエッジ26bとの距離L2およびメタル配線パターン24のエッジ24dとビアホールパターン26のエッジ26dとの距離L4がともにLminである場合には、エッジ26bとエッジ26dを固定し、他のエッジ26a、26cをそれぞれエッジ24a、24cの方向に移動してビアホールパターン26の寸法を大きくして、プロセス裕度を基準値より大きくする。

### [0067]

以上説明したように、上述の変形例1では、複数の露光マクスに跨がり、且つ、近接して配置されるメタル配線とビアホールから構成される配線パターンを抽出して、その配線パターン間の距離に応じたパターンの補正を行うことにより、配線パターン間のプロセス裕度が向上する。従って、半導体基板への配線パターンの転写精度が向上し、半導体装置の製造が容易になる。

### [0068]

なお、ここでは、L2、L4がLminの場合にエッジ26a、26cを補正する場合について説明したが、補正の対象となるエッジは、上述した場合に限定されるものではなく、各エッジ間の距離L1、L2、L3、L4が最小デザインルールLminより大きい条件を満たす範囲で移動するエッジを種々選択しても構わない。

### [0069]

### (第1の実施の形態の変形例2)

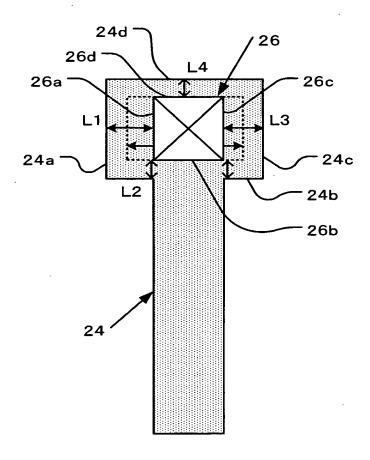

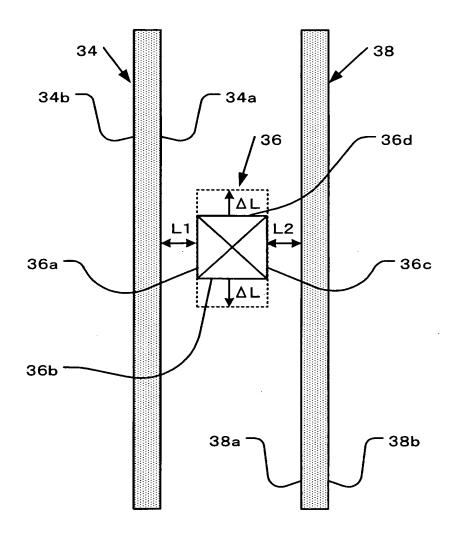

図5は、本発明の第1の実施の形態の変形例2を示す配線パターンである。本変形例が第1の実施の形態と異なる点は、2つのゲート配線ラインに挟まれてコンタクトホールが形成されるパターンとしたことにあり、第2の露光マスク13に2つのゲート配線パターン34、38が、第3の露光マスク15にコンタクトホールパターン36が形成されている。なお、本変形例においては、第1の実施の形態に対応させてゲート配線パターンが設けられる露光マスクを第2の露光マスク、またコンタクトホールが形成される露光マスクを第3の露光マスクと呼称しているが、3枚の露光マスクが存在するのではなく、2枚の露光マスクからなる。

#### [0070]

即ち、図5に示すように、リソグラフィー技術により、ゲート配線膜を形成した半導体基板の所定領域に第2の露光マスク13を用いて2つのゲート配線パターン34、38が加工され、次に、第3の露光マスク15を用いて2つのゲート配線ラインに挟まれたコンタクトホールパターン36が開口される。

#### [0071]

ここで、第2の露光マスク13のゲート配線パターン34、38の各エッジ34 a、38 a と第3の露光マスク15のコンタクトホールパターン36の各エッジ36 a、36 b、36 c、36 dとから構成される配線パターンにおいて、エッジ34 a とエッジ36 a の距離をL1、エッジ38 a とエッジ36 c の距離をL2とする。

#### [0072]

図1に示したフローチャートに従って、第3露光マスク15のコンタクトホールパターン36が露光工程でプロセス裕度が基準値より少ないと判断された場合には、露光マスク間の設計パターン距離(L1、L2)が求められ、その結果に基づいてプロセス裕度が基準値より広がるように新しいパターンを形成するのための補正処理が行われる。

### [0073]

例えば、ゲート配線パターン34のエッジ34aとコンタクトホールパターン36のエッジ36aの距離L1およびゲート配線パターン38のエッジ38aとコンタクトホールパターン36のエッジ36cの距離L2がLminである場合には、エッジ36a、36cを固定して、他のエッジ36b、36dをエッジ34a、38aと平行な方向へ移動させてコンタクトホールパターン36の寸法を大きくして、プロセス裕度を基準値より大きくする。

### [0074]

以上説明したように、上述の変形例2では、複数の露光マクスに跨がり、且つ、近接して配置される2つのゲート配線ラインと、その間に挟まれたコンタクトホールから構成される配線パターンを抽出して、その配線パターン間の距離に応じたパターンの補正を行うことにより、配線パターン間のプロセス裕度が向上する。従って、半導体基板への配線パターンの転写精度が向上し、半導体装置の製造が容易になる。

### [0075]

### (第1の実施の形態の変形例3)

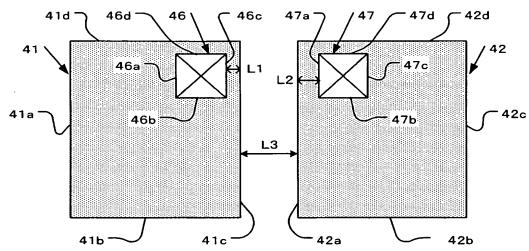

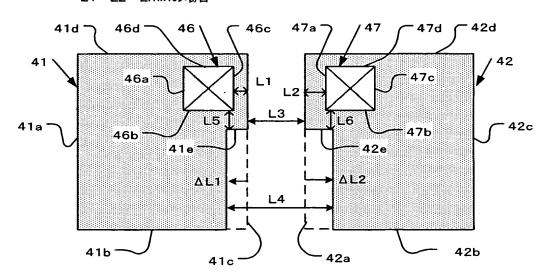

図6は、本発明の第1の実施の形態の変形例3を示す配線パターンで、図6(a)は配線パターンの補正前の状態を示すレイアウト図、図6(b)は図6(a)に示した配線パターンの補正後の状態を示すレイアウト図である。

#### [0076]

本変形例が第1の実施の形態と異なる点は、近接して配置された2つのイオン 注入拡散層にそれぞれコンタクトホールが形成されるパターンとしたことである

#### [0077]

即ち、第1の露光マスク11に2つのイオン注入拡散層パターン41、42が配置され、第3の露光マスク15に2つのコンタクトホールパターン46、47が配置されている。なお、本変形例においては、第1の実施の形態に対応させて拡散層パターンが設けられる露光マスクを第1の露光マスク、またコンタクトホールパターンが形成される露光マスクを第3の露光マスクと呼称しているが、3枚の露光マスクが存在するのではなく、2枚の露光マスクからなる。

図6 (a) に示すように、リソグラフィー技術により、レジスト膜を形成した 半導体基板の所定領域に、第1の露光マスク11を用いて2つのイオン注入パタ ーン41、42が開口した後、イオン注入および活性化処理がなされ、次に、半 導体基板に絶縁膜を形成した後、第3の露光マスク15を用いて絶縁膜に2つの コンタクトホールパターン46、47が開口される。

### [0079]

ここで、イオン注入パターン41の各エッジ41a、41b、41c、41dと、イオン注入パターン42の各エッジ42a、42b、42c、42d、およびコンタクトホールパターン46の各エッジ46a、46b、46c、46dと、コンタクトホールパターン47の各エッジ47a、47b、47c、47dとから構成される配線パターンにおいて、エッジ41cとエッジ46cの距離をL1、エッジ42aとエッジ47aの距離をL2、エッジ41cとエッジ42aの距離をL3とする。

### [0080]

図1に示したフローチャートに従って、第1の露光マスク11の2つのイオン 注入パターン41、42がリソグラフィー工程でプロセス裕度が基準値より少な いと判断された場合には、露光マスク間の設計パターン距離(L1、L2、L3 )が求められ、その結果に基づいてプロセス裕度が基準値より広がるように新し いパターンを形成するのための補正処理が行われる。

### [0081]

例えば、図6(b)に示すように、イオン注入パターン41のエッジ41cとコンタクトホールパターン46のエッジ46cの距離L1およびイオン注入パターン42のエッジ42aとコンタクトホールパターン47のエッジ47aの距離L2がLminである場合には、エッジ41cとエッジ42aの一部をイオン注入パターン41、42の内側に移動させて、エッジ41cとエッジ42aの距離をL3からL4に拡げて、プロセス裕度を基準値より大きくする。

#### [0082]

ここで、エッジ41c、42aの移動量は、シミュレーションまたは実験によ

り定められ、パターン41、42とパターン46、47の最小デザインルールを 維持するために、エッジ46bとエッジ41eの距離L5およびエッジ47bと エッジ42eの距離L6はLminより大きく設定される。

### [0083]

以上説明したように、上述の変形例3では、複数の露光マクスに跨がり、且つ、近接して配置される2つのイオン注入拡散層とコンタクトホールから構成される配線パターンを抽出して、その配線パターン間の距離に応じたイオン注入パターンの補正を行うことにより、配線パターン間のプロセス裕度が向上する。従って、半導体基板への配線パターンの転写精度が向上し、半導体装置の製造が容易になる。

### [0084]

#### (第2の実施の形態)

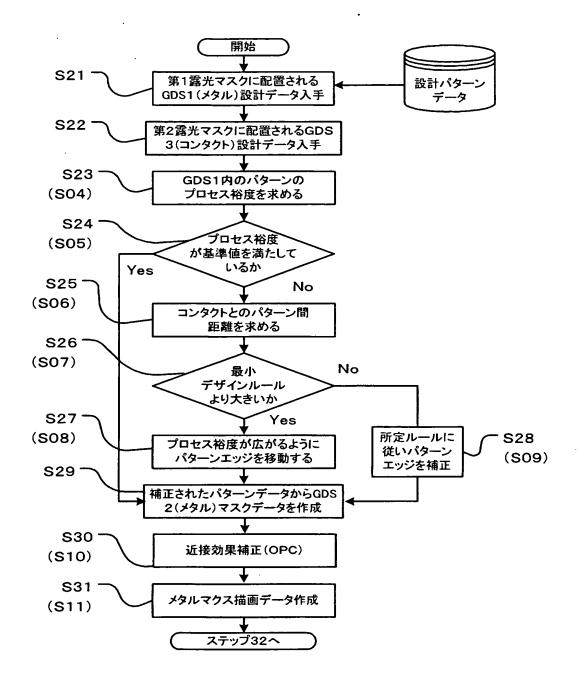

図7および図8は、本発明の第2の実施の形態に係わるパターン作成方法で、 設計パターンデータから露光マクス描画データが作成されるまでの工程を示すフローチャートである。本実施の形態において、上記第1の実施の形態と同一の構成部分には、同一符号を付してその説明を省略し、異なる部分のみ説明する。

#### [0085]

本実施の形態が第1の実施の形態と異なる点は、第1および第2の露光マスクに配置される配線パターンが共にプロセス裕度が少ないと判定された場合に、第1および第2ターゲットパターンの両方のパターンを補正することである。

#### [0086]

図7に示すように、所定のデザインルールに従って、第1の露光マクスに配置される設計パターンデータ(GDS1と称する)を設計パターンデータ記憶装置から入手し(ステップS21)、続いて、第2の露光マクスに配置される設計パターンデータ(GDS3と称する)を入手する(ステップS22)。

#### [0087]

次に、図1に示したフローチャートのステップS04からステップS09と同様にして、GDS1から任意の配線パターンを選出して、そのプロセス裕度を求め、プロセス裕度が基準値より広がるようにパターンエッジが移動される(ステ

ップS23からステップS28)。

### [0088]

次に、この補正された結果を基に、GDS1の新しい露光マスクデータ(GDS2と称する)が作成される(ステップS29)。

### [0089]

次に、図1に示したフローチャートのステップS10からステップS11と同様にして、補正後の配線パターンの必要な箇所に対して、OPCパターンを付与して、近接効果補正をおこない、GDS1の露光マスク描画データを得る(ステップS30からステップS31)。

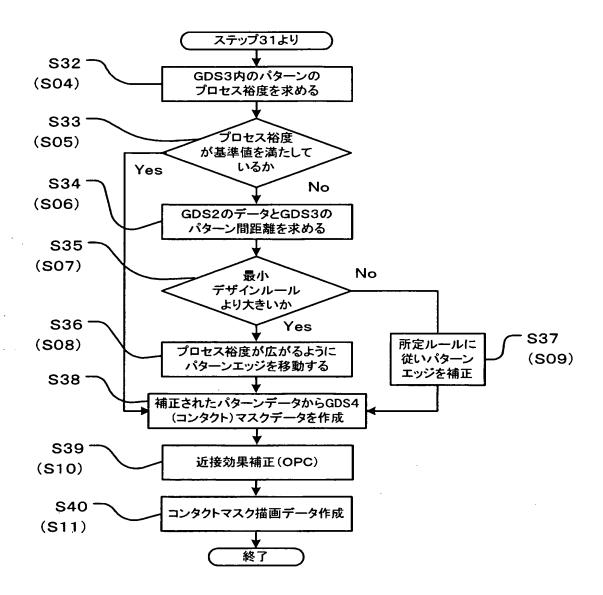

#### [0090]

次に、図8に示すように、図1に示したフローチャートのステップS04からテップS09と同様にして、GDS3からステップS23で選出されたGDS1のパターンに対応するパターンを選出して、そのプロセス裕度を求め、プロセス裕度が基準値より広がるようにパターンエッジが移動される(ステップS32からステップS37)。

#### [0091]

ここでの違いは、ステップS29で作成されたGDS2を用いて、GDS2とGDS3のパターン間の距離を求めることである(ステップS34)。

#### [0092]

次に、この補正された結果を基に、GDS3の新しい露光マスクデータ(GDS4と称する)が作成される(ステップS38)。

#### [0093]

最後に、図1に示したフローチャートのステップS10からステップS11と 同様にして、補正後の配線パターンの必要な箇所に対して、OPCパターンを付 与して、近接効果補正をおこない、GDS3の露光マスク描画データを得る(ス テップS39からステップS40)。

#### [0094]

さらに、上述したパターン形成工程は、設計データGDS1、GDS3にある 全ての配線パターンに対して繰り返され、最終的に露光マスク描画データとなる

0

次に、上述のパターン作成方法により配線パターンを補正し、プロセス裕度を 改善する場合について、具体的に説明する。

#### [0096]

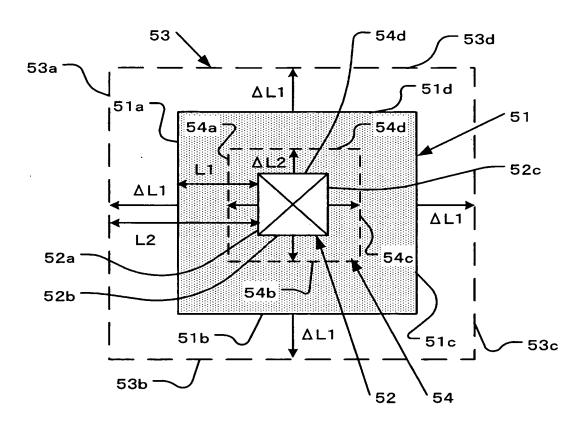

図9は、2枚の露光マスクを重ね合わせて得られる配線パターンの要部を示す 図で、メタル電極とコンタクトホールパターンが同芯相似形に重なって配置され たパターンの例である。

#### [0097]

図に示すように、第1の露光マスク11にGDS1として、例えばメタル電極パターン51と、第2の露光マスク13にGDS3として、例えばコンタクトホールパターン52がそれぞれ配置されている。

### [0098]

即ち、図に示すように、リソグラフィー技術により、半導体基板に金属膜を形成した後、第1の露光マスク11を用いてメタル電極パターン51が形成され、次に、半導体基板に絶縁膜を形成した後、第2の露光マスク13を用いて絶縁膜にコンタクトホールパターン52が開口される。

### [0099]

ここで、メタル電極パターン51のエッジ51aとコンタクトホールパターン52のエッジ52aの距離をL1とする。

### [0100]

図7に示したフローチャートに従い、第1露光マスク11のメタル電極パターン51が、リソグラフィー工程でプロセス裕度が基準値より少ないと判断された場合には、メタル電極パターン51の各エッジ51a、51b、51c、51dを $\Delta$ L1だけ外側へ移動して、メタル電極パターン51の寸法を大きくすることにより、プロセス裕度を基準値より大きくする。

#### $[0\ 1\ 0\ 1]$

これにより想像線で示す補正された新しいメタル電極パターン(GDS2)5 3が得られ、これを基に第1の露光マクス描画データが作成される。

### [0102]

同様に、図8に示したフローチャートに従い、第2の露光マスク13のコンタクトホールパターン52がリソグラフィー工程でプロセス裕度が基準値より少ないと判断された場合には、露光マスク間の設計パターン距離L1を求め、その結果に基づいてプロセス裕度が広がるように新しいパターンを形成するための補正処理が行われる。

### [0103]

例えば、メタル電極パターン51のエッジ51aとコンタクトホールパターン52のエッジ52aの距離L1がLminである場合には、エッジ52aを移動することは出来ないため、上述した補正された新しいメタル電極パターン(GDS2)53のエッジ53aとコンタクトホールパターン52のエッジ52aとの距離L2を測定して、コンタクトホールパターン52の各エッジ52a、52b、52c、52dを外側に $\Delta$ L2だけ移動してコンタクトホールパターン52の寸法を大きくすることにより、プロセス裕度を基準値より大きくする。

### [0104]

これにより想像線で示す補正された新しいコンタクトホールパターン(GDS4)54が得られ、これを基に第2の露光マクス描画データが作成される。

#### $[0\ 1\ 0\ 5]$

以上説明したように、本発明の第2の実施の形態に係わるパターン作成方法では、2つの露光マクスに跨って形成され、且つ、同芯相似形に配置される配線パターン間の距離に応じたパターンの補正を行うことにより、配線パターン間のプロセス裕度が向上する。従って、半導体基板への配線パターンの転写精度が向上し、半導体装置の製造が容易になる。

### [0106]

#### (第3の実施の形態)

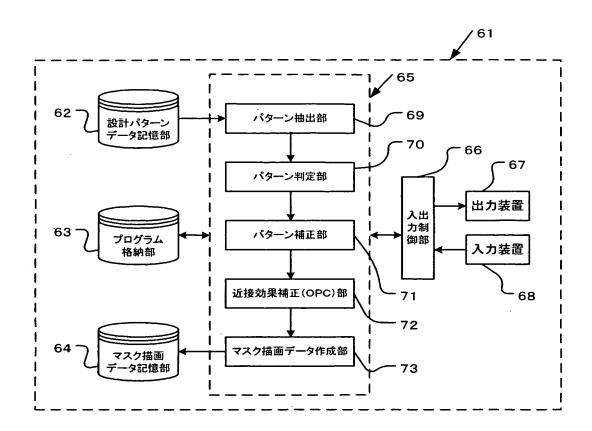

次に、本発明の第3の実施の形態に係わるパターン作成システムについて、図 10を用いて説明する。本実施の形態のパターン作成システムは、第1および第 2の実施の形態で示したパターン作成方法を実現するためのものである。

#### [0107]

図10は、本発明のパターン作成システムの構成を示すブロック図である。

### [0108]

図に示すように、本発明のパターン作成システム61は、半導体装置のレイアウト設計パターンデータを格納した設計パターンデータ記憶部62と、露光マクスパターンを補正して新しいパターンを形成するプログラムなどを格納したプログラム格納部63、得られた露光マスク描画データを格納するマクス描画データ記憶部64と、一連のマクスパターン補正処理を実行するための手段を備えた処理制御部65と、入出力制御部66を介して処理結果を出力する出力装置67と、処理制御部65への指示等を入力する入力装置68とで構成されている。

#### $[0\ 1\ 0\ 9]$

設計パターンデータ記憶部62、プログラム格納部63、および露光マスク描画データ記憶部64は、一部はコンピュータ内部の主記憶装置で構成しても良いし、このコンピュータに接続された半導体メモリー、磁気ディスク、磁気テープ、光ディスクなどの記憶装置で構成しても構わない。

### [0110]

また、処理制御部65は、コンピュータシステムの中央演算処理装置の一部を 構成しており、集中処理方式または分散処理方式のコンピュータシステムで実行 される。

#### [0111]

この処理制御部65は、第1および第2の露光マスクに配置される配線パターンを設計パターンデータ記憶部62から読み込んで、第1および第2の露光マスクに配置される配線パターンの中から、第1および第2のターゲットパターンを抽出するパターン抽出部69と、露光パラメータの変動に対してプロセス裕度が予め定めた基準値を満たすか否かを判定するパターン判定部70と、基準値を満たさないと判定されたパターンのプロセス裕度を拡大するようにパターンを補正するパターン補正部71と、補正後の設計パターンの必要な箇所に対して、OPCパターンを付与して、近接効果補正(OPC)をおこなう近接効果補正部72と、プロセス裕度が基準値より改善され、且つ、近接効果補正がなされた最終のパターンを露光マスク上に形成するための露光マスク描画データを作成するマク

ス描画データ作成部73から構成されている。

#### $[0\ 1\ 1\ 2]$

これらのパターン抽出部69、パターン判定部70、パターン補正部71、近接効果補正部72、マクス描画データ作成部73は、ソフトウェアとしてプログラム格納部63に予め格納されており、その手順に従ってコンピュータシステムの中央演算処理装置にて実行されるが、専用のハードウェーアで実行されるものでも構わない。

### [0113]

以上説明したように、本発明のパターン作成システムによれば、複数の露光マクスに跨って形成され、且つ、近接して配置される配線パターン間の距離に応じたパターンの補正を行うことにより、プロセス裕度の高い配線パターンを有する露光マスクが得られる。

### [0114]

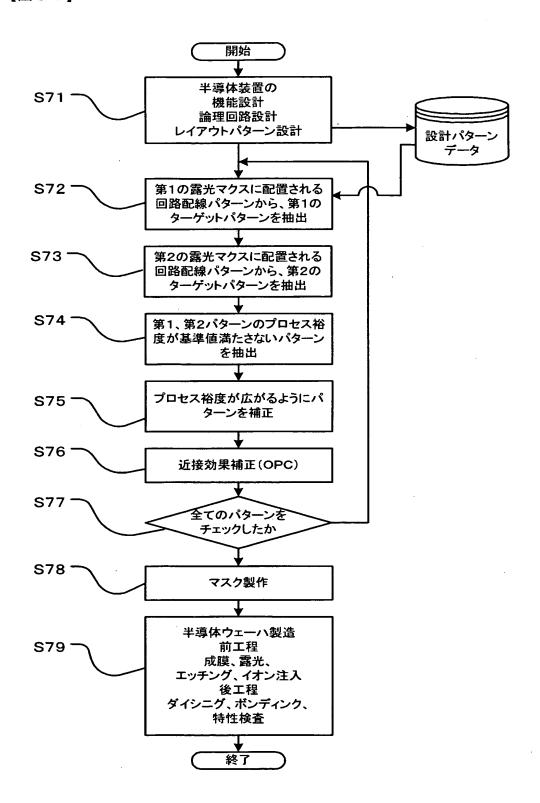

#### (第4の実施の形態)

次に、本発明の第4の実施の形態に係わる半導体装置の製造方法について、図 11を用いて説明する。本実施の形態の半導体装置の製造方法は、第3の実施の 形態で示したパターン作成システムを用いて、半導体装置を製造する場合の例で ある。図11は、本発明の半導体装置の製造方法を示すフローチャートである。

#### [0115]

まず、製造する半導体装置の機能設計、論理回路設計およびレイアウトパターン設計が行われる(ステップS71)。

#### $[0\ 1\ 1\ 6\ ]$

即ち、製造する半導体装置の目的や作用効果を実現するために必要な機能を明らかにし、その機能を生み出すためのロジック・メモリ、入出力インターフェイスなどの各部の機能と互いのつながりを設計する機能設計が行われる。

#### [0117]

次に、各部の機能および相互関係から具体的な電子回路を設計する論理回路設計が行われる。そして、各電子回路を半導体チップ上にどのように配置するかレイアウト設計が行われ、半導体ウェーハの一連の製造工程で使用される複数の露

光マスク上に配置される配線パターンがデザインルールを満たすように設計される。

#### [0118]

このレイアウトの設計パターンデータは、設計パターン記憶部に送られ、第1 および第2の実施の形態で説明したプロセス裕度が基準値より少ない配線パターンを抽出して、プロセス裕度が基準値より広がるように配線パターンの補正が行われる。

### [0119]

即ち、第1の露光マスクに配置される配線パターンの中から第1のターゲットパターンを抽出し(ステップS72)、第2の露光マスクに配置される配線パターンの中から第1のターゲットパターンと近接して配置される第2のターゲットパターンが抽出される(ステップS73)。

### [0120]

次に、第1ターゲットパターンと第2ターゲットパターンのプロセス変動に対するプロセス裕度が予め与えられた基準値を満たさないパターンが抽出され(ステップS74)、プロセス裕度が広がるように第1または第2ターゲットパターンのエッジを移動してパターンが補正される(ステップS75)。

#### $[0 \ 1 \ 2 \ 1]$

次に、補正後の設計パターンの必要な部分に対して近接効果補正(OPC)パターンを付加して近接効果が補正される(ステップS76)。

#### [0122]

次に、全ての配線パターンに対してプロセス裕度がチェックされるまで上述した工程が繰り返される(ステップS77)。

### [0123]

次に、プロセス裕度改善と近接効果補正がなされた最終バターンを露光マスク 上に形成するための露光マスク描画データが作成され、これに基づいて露光マス クが製作される(ステップS78)。

#### [0124]

次に、半導体基板に対して絶縁膜、半導体膜、金属膜などの成膜工程、上述し

た露光マスクを用いたリソグラフィー工程、エッチング工程、イオン注入工程などを繰り返す一連のウェーハ製造工程(前工程)により、半導体ウェーハ上に半導体装置が一括して形成される。そして、ダイシング工程、ボンディング工程、検査工程(後工程)を経て、半導体装置が製造される(ステップS79)。

### [0125]

以上説明したように、本発明の半導体装置の製造方法によれば、配線パターン間のプロセス裕度の高い露光マスクにより半導体基板へ配線パターンが転写できるので、高い歩留まりで半導体装置を製造することができる。

### [0126]

### 【発明の効果】

以上説明したように、本発明によれば、複数の露光マスクに跨って配置される 配線パターン間のプロセス裕度を向上し得るパターン作成方法、該パターン形成 システムを提供することができる。また、該パターンを用いた半導体装置の製造 方法によれば、高い歩留まりを提供することができる。

### 【図面の簡単な説明】

- 【図1】 本発明の第1の実施の形態に係わるパターン作成方法を示すフローチャート。

- 【図2】 本発明の第1の実施の形態に係わる露光マクスを示す図で、図2 (a) は複数の露光マスクにそれぞれ形成されるパターンの要部を示す外観図、図2 (b) は図2 (a) の配線パターンを示す図。

- 【図3】 本発明の第1の実施の形態に係わる配線パターンを示す図。

- 【図4】 本発明の第1の実施の形態の変形例1に係わる配線パターンを示す図

- 【図5】 本発明の第1の実施の形態の変形例2に係わる配線パターンを示す図

- 【図6】 本発明の第1の実施の形態の変形例3に係わる配線パターンを示す図で、図6(a)は配線パターンの補正前の状態を示すレイアウト図、図6(b)・は図6(a)に示した配線パターンの補正後の状態を示すレイアウト図。

- 【図7】 本発明の第2の実施の形態に係わるパターン作成方法を示すフローチ

ヤート。

- 【図8】 本発明の第2の実施の形態に係わるパターン作成方法を示すフローチャート。

- 【図9】 本発明の第2の実施の形態に係わる配線パターンを示す図。

- 【図10】 本発明の第3の実施の形態に係わるパターン作成システムを示すブロック図。

- 【図11】 本発明の第4の実施の形態に係わる半導体装置の製造方法を示すフローチャート。

- 【図12】 従来のパターン作成方法を示す概略フローチャート。

- 【図13】 従来のパターン作成方法により補正された配線パターンを示す図。

### 【符号の説明】

- 11 第1の露光マスク

- 12、41、42 イオン注入パターン

- 12a, 12b, 12c, 12d, 41a, 41b, 41c, 41d, 42a,

- 42b、42c、42d イオン注入パターンのエッジ

- 13 第2の露光マスク

- 14、34、38 ゲート配線パターン

- 14a、14b、34a、34b、38a、38b ゲート配線パターンのエッジ

- 15 第3の露光マスク

- 16、36、46、47、52、54 コンタクトホールパターン

- 16a, 16b, 16c, 16d, 36a, 36b, 36c, 36d, 46a,

- 46b, 46c, 46d, 47a, 47b, 47c, 47d, 52a, 52b,

- 52c、52d、54a、54b、54c、54d コンタクトホールパターン のエッジ

- 24 メタル配線パターン

- 24a、24b、24c、24d メタル配線パターンのエッジ

- 26 ビアホールパターン

- 26a、26b、26c、26d ビアホールパターンのエッジ

- 34 a、38 a ゲート配線パターンのエッジ

- 51、53 メタル電極パターン

- 51a、51b、51c、51d、53a、53b、53c、53d メタル電

### 極パターンのエッジ

- 61 パターン形成システム

- 62 補正処理制御部

- 63 設計パターンデータ記憶部

- 64 プログラム格納部

- 65 露光マスク描画データ記憶部

- 6 6 入出力制御部

- 67 出力部

- 68 入力部

- 69 パターン抽出部

- 70 パターン判定部

- 71 パターン変更部

- 72 近接効果補正部

- 73 露光マスク描画データ作成部

## 【書類名】 図面

### 【図1】

## 【図2】

11・・・第1の露光マスク

12・・・イオン注入パターン

13・・・第2の露光マスク

14・・・ゲート配線パターン

15・・・第3の露光マスク

16・・・コンタクトホールパターン

12a、12b、12c、12d····イオン注入パターンのエッジ

14a、14b・・・ゲート配線パターンのエッジ

16a、16b、16c、16d・・・コンタクトホールパターンのエッジ

## 【図3】

L1=Lmin, L2, L3, L4>Lmin の場合

L3=Lmin, L1, L2, L4>Lmin の場合

## 【図4】

### L1、L3>L2=L4=Lminの場合

24・・・メタル配線パターン

24a、24b、24c、24d・・・メタル配線パターンのエッジ

26・・・ビアホールパターン

26a、26b、26c、26d・・・ビアホールパターンのエッジ

【図5】

### L1=L2=Lminの場合

34、38・・・ゲート配線パターン 34a、34b、38a、38b・・・ゲート配線パターンのエッジ 36・・・コンタクトホールパターン 36a、36b、36c、36d・・・コンタクトホールパターンのエッジ

## 【図6】

#### (b) L1=L2=Lminの場合

41、42・・・イオン注入パターン

41a、41b、41c、41d、41e、42a、42b、42c、42d、42e・・・イオン注入パターンのエッジ

46、47・・・コンタクトホールパターン

46a、46b、46c、46d、47a、47b、47c、47d・・・コンタクトホールパターンのエッジ

## 【図7】

【図8】

## 【図9】

### L1=Lminの場合

51・・・メタル電極パターン

51a、51b、51c、51d・・・メタル電極パターンのエッヂ

52・・・コンタクトホールパターン

52a、52b、52c、52d・・・コンタクトホールパターンのエッジ

53・・・補正後のメタル電極パターン

53a、53b、53c、53d·・・補正後のメタル電極パターンのエッヂ

54・・・補正後のコンタクトホールパターン

54a、54b、54c、54d·・・補正後のコンタクトホールパターンのエッジ

## 【図10】

61・・・パターン形成システム 65・・・処理制御部

## 【図11】

## 【図12】

# 【図13】

### 【書類名】 要約書

### 【要約】

【課題】 複数の露光マスクに跨って配置される配線パターン間のプロセス裕度 を向上させる。

【解決手段】 第1の露光マスクに配置される配線パターンから第1のターゲットパターンを、また第2の露光マスクに配置される配線パターンから第1のターゲットパターンと近接して配置される第2のターゲットパターンをそれぞれ抽出 (S02,S03)、次に、第1および第2のターゲットパターンが、露光量と焦点距離の変動に対するプロセス裕度の基準値を満たすか否かを判定する (S05)、そして、この基準値を満たさない場合には、この基準値を満たすように第1および第2のターゲットパターンのいずれか一方、または両方のターゲットパターンを移動する (S08)。

### 【選択図】 図1

### 認定・付加情報

特許出願の番号

特願2003-110254

受付番号

5 0 3 0 0 6 2 1 8 5 5

書類名

特許願

担当官

第五担当上席 0094

作成日

平成15年 4月16日

<認定情報・付加情報>

【提出日】

平成15年 4月15日

特願2003-110254

出願人履歴情報

識別番号

[000003078]

1. 変更年月日

2001年 7月 2日

[変更理由]

住所変更

住 所

東京都港区芝浦一丁目1番1号

氏 名

株式会社東芝